CPU

- 程序控制功能,CPU通过执行指令来控制程序的执行顺序

- 操作控制

- 时间控制

- 数据处理,CPU最根本的任务

运算器

- 算术逻辑单元ALU:数据的算术和逻辑运算;

- 累加寄存器AC:通用寄存器,为ALU提供一个工作区,用在暂存数据;

- 数据缓冲寄存器DR:写内存暂存指令或数据;

- 状态条件寄存器PSW:存状态标志与控制标志;

控制器

分析和执行指令的部件

- 程序计数器PC:存储下一条要执行指令的地址;

- 指令寄存器IR:存储即将执行的指令;

- 指令译码器ID:对指令中的操作码字段进行分析解释;

- 地址寄存器AR:用来保存当前CPU所访问的内存单元的地址;

- 时序部件:提供时序控制信号;

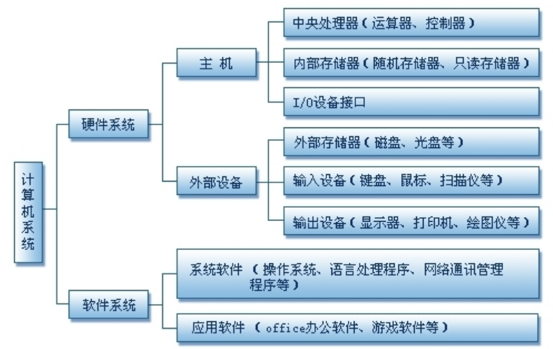

Flynn分类

根据指令流、数据流的多倍性特征对计算机系统进行分类:

- 指令流

指机器执行指令序列; - 数据流

指由指令流调用的数据序列,包括输入数据、中间结果,但不包括输出数据;

分成四类

- 单指令但数据流(SISD)

- 单指令多数据流(SIMD)

- 多指令但数据流(MISD),无实际用处。

- 多指令多数据流(MIMD)

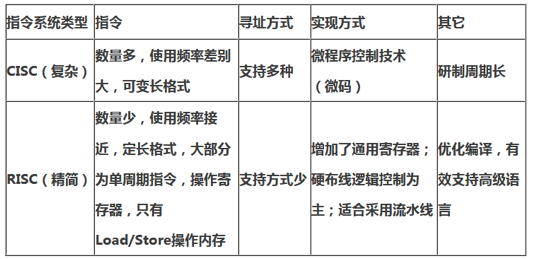

指令系统

复杂指令系统(CISC)

- 指令多,100~150条。

- 使用频率相差悬殊:20%指令出现80%,80%指令出现20%。

- 寻址方式多,5~20

- 指令长度不固定,增加指令译码电路复杂性。

- 指令可以直接处理存储单元数据,速度慢

- 以微程序控制为主。CISC的指令系统复杂,难以用硬布线逻辑电路实现控制器,通常采用微程序控制。

精简指令系统(RISC)

- 指令少

- 寻址方式少:

- 寄存器寻址方式

- 立即数寻址方式

- 相对寻址方式

- 指令长度固定、格式种类少。

- 以硬布线逻辑控制为主

- 单周期指令执行,采用流水线技术。

- 优化的编译器

- cpu中的通用寄存器数量多,一般32个以上,最高有上千个。

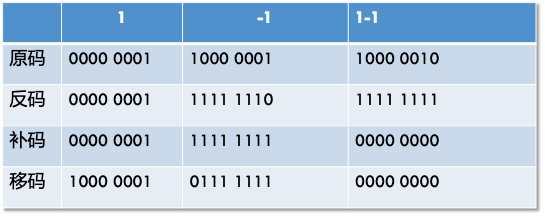

数据表示

- 补码是最适合进行数字加减运算的数字编码。

- 移码只用于表示浮点数的阶码,所以只用于整数。

码距

一个编码系统的码距就是整个编码系统中任意(所有)两个码字的最小距离。若一个码距有四种编码分别是:000,0011,1100,1111,此编码系统中0000 与 1111 的码距为4;0000 与0011的码距为2,是此编码系统的最小码距。因此该编码系统的码距为2.

- 检测e个误码,最小码距满足d>=e+1;

- 纠正t个误码,最小码距满足:d>=2t+1;

- 同时纠错检错:d>=e+t+1;

校验码

- 奇偶校验

只能检测代码中奇数位出错的编码,但不能发现偶数位出错的情况。 - 海明码

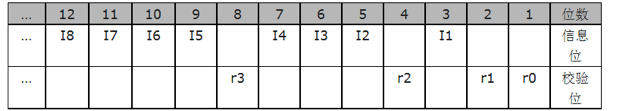

校验码位置必须是2n位置(n从0开始,1、2、4、8…)信息码在非2n位置

![]()

设n个数据位,k个校验位,满足:2^k≥n+k+1 - 循环冗余校验码CRC

指令

-

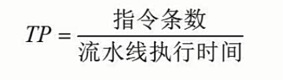

吞吐率

![]()

![]()

-

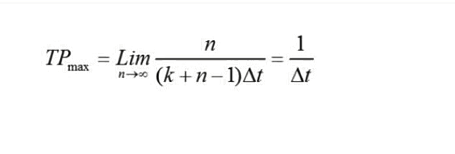

流水线加速比

![]()

-

流水线总时间:

理论公式:t1+t2+…+tk+(n-1)△t

实践公式:(K+n-1)*△t

* △t:流水线周期、执行时间最长一段;

* n 执行条数

* k 分几个部分

控制方式

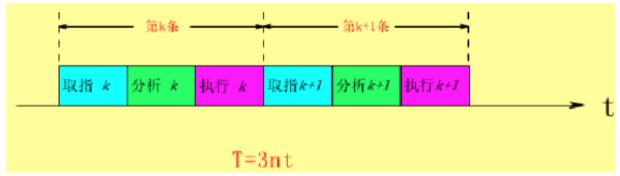

- 顺序方式

![]()

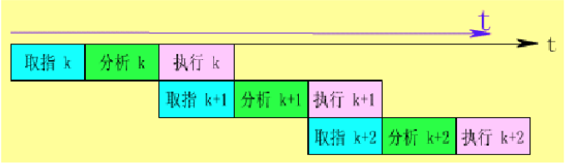

- 重叠方式

![]()

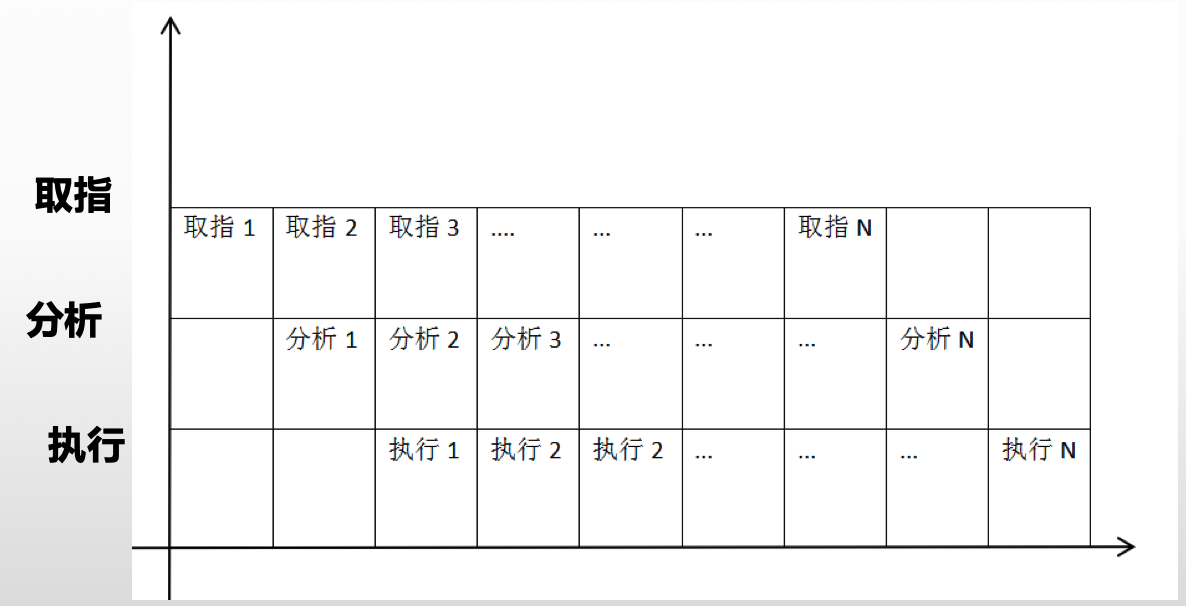

- 流水线

![]()

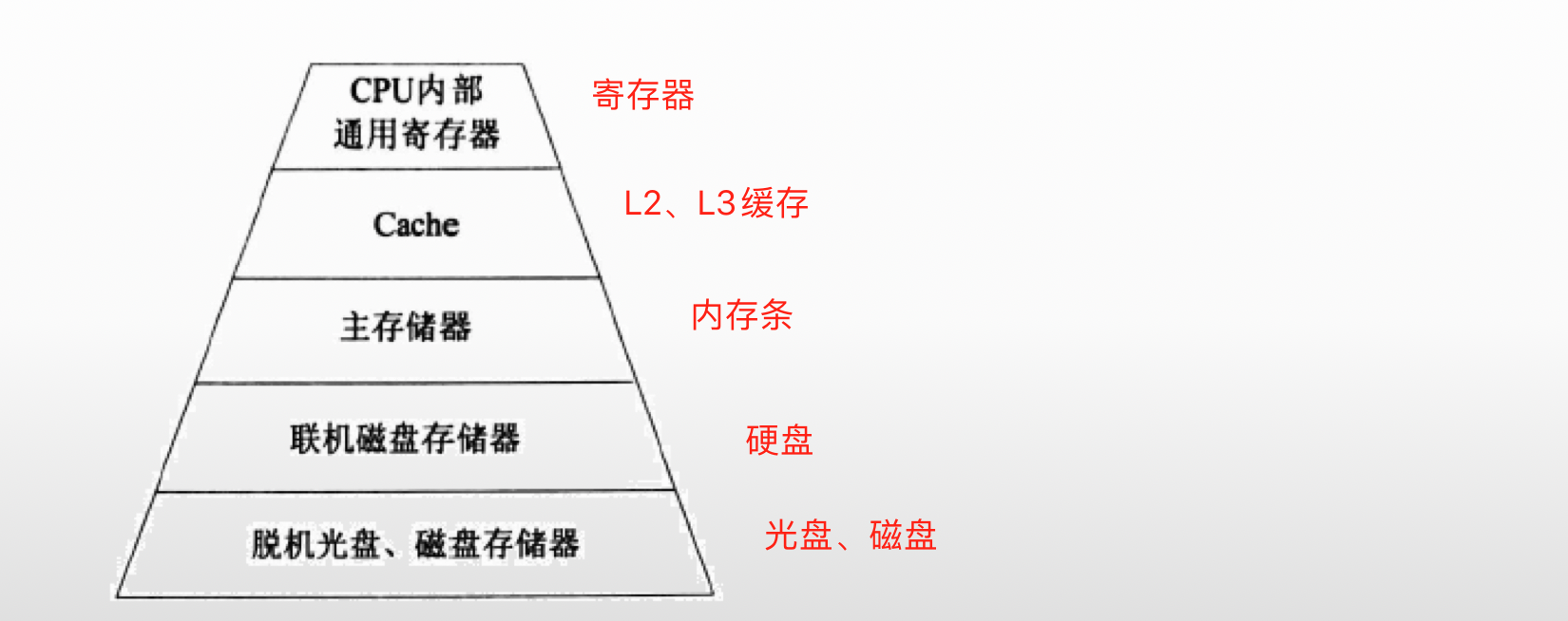

存储系统

寄存器

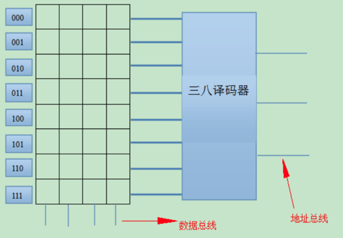

内存编址

存储器由多块存储单元组成,内存编址就是对存储单元进行标识。

芯片

存储器由若干个芯片构成

内存容量

内存容量=每个芯片容量 x 芯片个数

每个芯片容量=一个地址代表的容量 x 编址总数

数据总线

计算机一次处理n位的数据,则数据总线的长度为n。注意:数据总线的长度,并不代表一个地址的长度。

字

和数据总线紧密相关,数据总线有几位,则一个字就由多少位组成。如64位计算机,标识一次可以处理64位数据,则1个字就是64位。

地址总线

假如需要n位二进制数标识所有地址,则地址总线的个数为n

案例

【问题】

内存按字节编址,地址从A4000H到CBFFFH,共有 (1) 个字节。若用存储容量为32K×8bit的存储芯片构成该内存,至少需要 (2) 片。

【解答】

1.先求出地址总个数:CBFFFH-A4000H+1=28000H(十六进制)

2*(164)+8*(163)=163840=160*1024(个)=160K(个)

2.求解芯片个数

160KB/32KB=5(个)

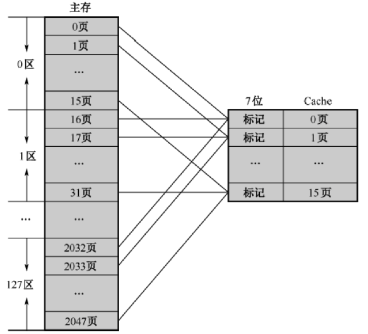

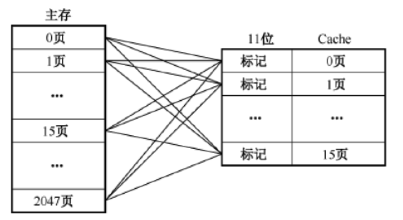

Cache

cache是为了解决高速运行的cpu与主存储器之间速度不匹配的问题。

cache的地址映像方法:

- 直接映像

![]()

- 全相连映像

![]()

- 组相连映像

![]()

cache性能

Hc代表cache的访问命中率,tc为cache的存取时间,tm为主存的访问时间,则Cache的平均访问时间ta为:

ta=Hc✖️ tc+(1-hc)✖️tm

主存一致性

- 写回法(write–back)

修改时 写入cache,当被换出时同步主存; - 写直达法(write–through)

又称 全写法,同时写cache、主存; - 标记法

修改时写入主存,cache中标记失效;

磁盘

案例

【解答】

未优化处理时间:(9×33ms+ 9ms=306ms)

优化后处理时间:10×(3ms(读记录)+6ms(处理记录))=10×9ms90ms

总线

总线是计算机各个功能部件之间传送信息的公共通信干线。

- 按照总线相对应芯片的位置分类:

- 内部总线

* 外部总线

- 内部总线

- 按照总线功能划分:

- 地址总线–传送地址信息

* 数据总线–传送数据信息

* 控制总线–传送控制信号、时序信号

- 地址总线–传送地址信息

- 按照总线在微机中的位置划分:

- 机内总心啊

* 机外总线

- 机内总心啊

- 按照总线功能划分:

- 局部总线

* 系统总线

* 通信总线

- 局部总线

- 按照总线内数据线的多少划分:

- 并行总线

* 串行总线

- 并行总线